一個布局是否合理沒有判斷標準,可以采用一些相對簡單的標準來判斷布局的優劣。最常用的標準就是使飛線總長度盡可能短。一般來說,飛線總長度越短,意味著布線總長度也是越短(注意:這只是相對于大多數情況是正確的,并不是完全正確);走線越短,走線所占據的印制板面積也就越小,布通率越高。在走線盡可能短的同時,還必須考慮布線密度的問題。如何布局才能使飛線總長度最短并且保證布局密度不至于過高而不能實現是個很復雜的問題。因為,調整布局就是調整封裝的放置位置,一個封裝的焊盤往往和幾個甚至幾十個網絡同時相關聯,減小一個網絡飛線長度可能會增長另一個網絡的飛線長度。如何能夠調整封裝的位置到最佳點實在給不出太實用的標準,實際操作時,主要依靠設計者的經驗觀查屏幕顯示的飛線是否簡捷、有序和計算出的總長度是否最短。飛線是手工布局和布線的主要參考標準,手工調整布局時盡量使飛線走最短路徑,手工布線時常常按照飛線指示的路徑連接各個焊盤。Protel的飛線優化算法可以有效地解決飛線連接的最短路徑問題。飛線的連接策略Protel提供了兩種飛線連接方式供使用者選擇:順序飛線和最短樹飛線。在布線參數設置中的飛線模式頁可以設置飛線連接策略,應該選擇最短樹策略。動態飛線在有關飛線顯示和控制一節中已經講到: 執行顯示網絡飛線、顯示封裝飛線和顯示全部飛線命令之一后飛線顯示開關打開,執行隱含全部飛線命令后飛線顯示開關關閉。

尤其在使用高速數據網絡時,攔截大量信息所需要的時間顯著低于攔截低速數據傳輸所需要的時間。數據雙絞線中的絞合線對在低頻下可以靠自身的絞合來抵抗外來干擾及線對之間的串音,但在高頻情況下(尤其在頻率超過250MHz以上時),僅靠線對絞合已無法達到抗干擾的目的,只有屏蔽才能夠抵抗外界干擾。電纜屏蔽層的作用就像一個法拉第護罩,干擾信號會進入到屏蔽層里,但卻進入不到導體中。因此,數據傳輸可以無故障運行。由于屏蔽電纜比非屏蔽電纜具有較低的輻射散發,因而防止了網絡傳輸被攔截。屏蔽網絡(屏蔽的電纜及元器件)能夠顯著減小進入到周圍環境中而可能被攔截的電磁能輻射等級。不同干擾場的屏蔽選擇干擾場主要有電磁干擾及射頻干擾兩種。電磁干擾(EMI)主要是低頻干擾,馬達、熒光燈以及電源線是通常的電磁干擾源。射頻干擾(RFI)是指無線頻率干擾,主要是高頻干擾。無線電、電視轉播、雷達及其他無線通訊是通常的射頻干擾源。對于抵抗電磁干擾,選擇編織屏蔽最為有效,因其具有較低的臨界電阻;對于射頻干擾,箔層屏蔽最有效,因編織屏蔽依賴于波長的變化,它所產生的縫隙使得高頻信號可自由進出導體;而對于高低頻混合的干擾場,則要采用具有寬帶覆蓋功能的箔層加編織網的組合屏蔽方式。通常,網狀屏蔽覆蓋率越高,屏蔽效果就越好。

1. 如果是人工焊接,要養成好的習慣,首先,焊接前要目視檢查一遍PCB板,并用萬用表檢查關鍵電路(特別是電源與地)是否短路;其次,每次焊接完一個芯片就用萬用表測一下電源和地是否短路;此外,焊接時不要亂甩烙鐵,如果把焊錫甩到芯片的焊腳上(特別是表貼元件),就不容易查到。2. 在計算機上打開PCB圖,點亮短路的網絡,看什么地方離的最近,最容易被連到一塊。特別要注意IC內部短路。3. 發現有短路現象。拿一塊板來割線(特別適合單/雙層板),割線后將每部分功能塊分別通電,一部分一部分排除。4. 使用短路定位分析儀,如:新加坡PROTEQ CB2000短路追蹤儀,香港靈智科技QT50短路追蹤儀,英國POLAR ToneOhm950多層板路短路探測儀等等。5. 如果有BGA芯片,由于所有焊點被芯片覆蓋看不見,而且又是多層板(4層以上),因此最好在設計時將每個芯片的電源分割開,用磁珠或0歐電阻連接,這樣出現電源與地短路時,斷開磁珠檢測,很容易定位到某一芯片。由于BGA的焊接難度大,如果不是機器自動焊接,稍不注意就會把相鄰的電源與地兩個焊球短路。

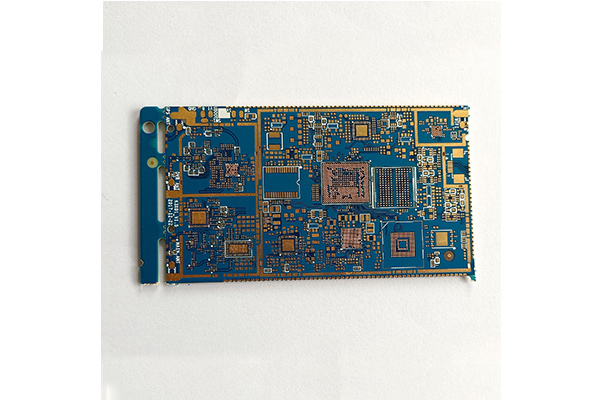

湖北廠家電路板組裝測試通訊與計算機技術的高速發展使得高速PCB設計進入了千兆位領域,新的高速器件應用使得如此高的速率在背板和單板上的長距離傳輸成為可能,電路板組裝測試生產商但與此同時,PCB設計中的信號完整性問題(SI)、電源完整性以及電磁兼容方面的問題也更加突出。信號完整性是指信號在信號線上傳輸的質量,主要問題包括反射、振蕩、時序、地彈和串擾等。信號完整性差不是由某個單一因素導致,而是板級設計中多種因素共同引起。在千兆位設備的PCB板設計中,一個好的信號完整性設計要求工程師全面考慮器件、傳輸線互聯方案、電源分配以及EMC方面的問題。高速PCB設計EDA工具已經從單純的仿真驗證發展到設計和驗證相結合,幫助設計者在設計早期設定規則以避免錯誤而不是在設計后期發現問題。隨著數據速率越來越高設計越來越復雜,高速PCB系統分析工具變得更加必要,這些工具包括時序分析、信號完整性分析、設計空間參數掃描分析、EMC設計、電源系統穩定性分析等。這里我們將著重討論在千兆位設備PCB設計中信號完整性分析應考慮的一些問題。高速器件與器件模型盡管千兆位發送與接收元器件供應商會提供有關芯片的設計資料,但是器件供應商對于新器件信號完整性的了解也存在一個過程,這樣器件供應商給出的設計指南可能并不成熟,還有就是器件供應商給出的設計約束條件通常都是非常苛刻的,對設計工程師來說要滿足所有的設計規則會非常困難。所以就需要信號完整性工程師運用仿真分析工具對供應商的約束規則和實際設計進行分析,考察和優化元器件選擇、拓撲結構、匹配方案、匹配元器件的值,并最終開發出確保信號完整性的PCB布局布線規則。因此,千兆位信號的精確仿真分析變得十分重要,而器件模型在信號完整性分析工作中的作用也越來越得到重視。