在基于信號完整性計算機(jī)分析的PCB設(shè)計方法中,最為核心的部分就是PCB板級信號完整性模型的建立,這是與傳統(tǒng)的設(shè)計方法的區(qū)別之處。SI模型的正確性將決定設(shè)計的正確性,而SI模型的可建立性則決定了這種設(shè)計方法的可行性。目前構(gòu)成器件模型的方法有兩種:一種是從元器件的電學(xué)工作特性出發(fā),把元器件看成‘黑盒子’,測量其端口的電氣特性,提取器件模型,而不涉及器件的工作原理,稱為行為級模型。這種模型的代表是IBIS模型和S參數(shù)。其優(yōu)點(diǎn)是建模和使用簡單方便,節(jié)約資源,適用范圍廣泛,特別是在高頻、非線性、大功率的情況下行為級模型是一個選擇。缺點(diǎn)是精度較差,一致性不能保證,受測試技術(shù)和精度的影響。另一種是以元器件的工作原理為基礎(chǔ),從元器件的數(shù)學(xué)方程式出發(fā),得到的器件模型及模型參數(shù)與器件的物理工作原理有密切的關(guān)系。SPICE 模型是這種模型中應(yīng)用最廣泛的一種。其優(yōu)點(diǎn)是精度較高,特別是隨著建模手段的發(fā)展和半導(dǎo)體工藝的進(jìn)步和規(guī)范,人們已可以在多種級別上提供這種模型,滿足不同的精度需要。缺點(diǎn)是模型復(fù)雜,計算時間長。一般驅(qū)動器和接收器的模型由器件廠商提供,傳輸線的模型通常從場分析器中提取,封裝和連接器的模型即可以由場分析器提取,又可以由制造廠商提供。在電子設(shè)計中已經(jīng)有多種可以用于PCB板級信號完整性分析的模型,其中最為常用的有三種,分別是SPICE、IBIS和Verilog-AMS、VHDL-AMS。

(一) 畫好原理圖很多工程師都覺得layout工作更重要一些,原理圖就是為了生成網(wǎng)表方便PCB做檢查用的。其實(shí),在后續(xù)電路調(diào)試過程中原理圖的作用會更大一些。無論是查找問題還是和同事交流,還是原理圖更直觀更方便。另外養(yǎng)成在原理圖中做標(biāo)注的習(xí)慣,把各部分電路在layout的時候要注意到的問題標(biāo)注在原理圖上,對自己或者對別人都是一個很好的提醒。層次化原理圖,把不同功能不同模塊的電路分成不同的頁,這樣無論是讀圖還是以后重復(fù)使用都能明顯的減少工作量。使用成熟的設(shè)計總是要比設(shè)計新電路的風(fēng)險小。每次看到把所有電路都放在一張圖紙上,一片密密麻麻的器件,腦袋就能大一圈。(二) 好好進(jìn)行電路布局心急的工程師畫完原理圖,把網(wǎng)表導(dǎo)入PCB后就迫不及待的把器件放好,開始拉線。其實(shí)一個好的PCB布局能讓你后面的拉線工作變得簡單,讓你的PCB工作的更好。每一塊板子都會有一個信號路徑,PCB布局也應(yīng)該盡量遵循這個信號路徑,讓信號在板子上可以順暢的傳輸,人們都不喜歡走迷宮,信號也一樣。如果原理圖是按照模塊設(shè)計的,PCB也一樣可以。按照不同的功能模塊可以把板子劃分為若干區(qū)域。模擬數(shù)字分開,電源信號分開,發(fā)熱器件和易感器件分開,體積較大的器件不要太靠近板邊,注意射頻信號的屏蔽等等……多花一分的時間去優(yōu)化PCB的布局,就能在拉線的時候節(jié)省更多的時間。

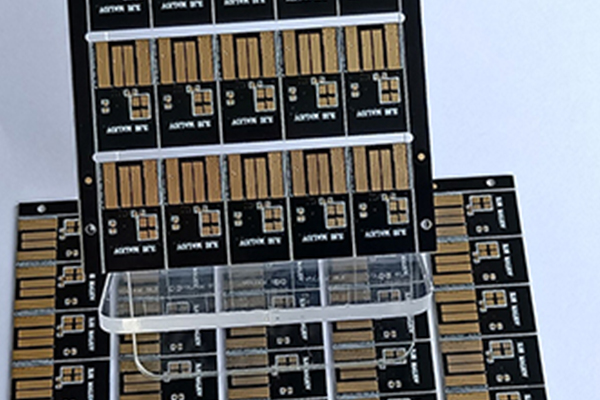

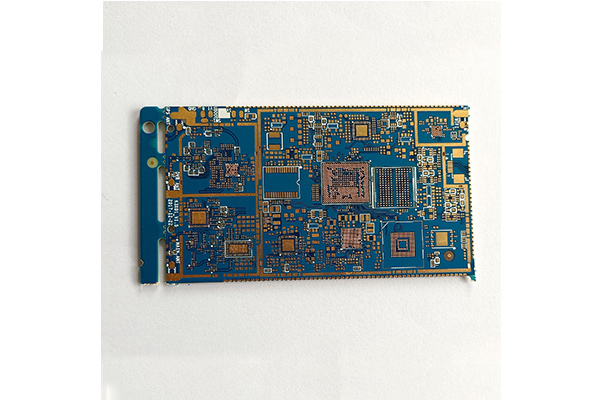

1.開料目的:根據(jù)工程資料MI的要求,在符合要求的大張板材上,裁切成小塊生產(chǎn)板件.符合客戶要求的小塊板料.流程:大板料→按MI要求切板→鋦板→啤圓角磨邊→出板鉆孔目的:根據(jù)工程資料,在所開符合要求尺寸的板料上,相應(yīng)的位置鉆出所求的孔徑.流程:疊板銷釘→上板→鉆孔→下板→檢查修理沉銅目的:沉銅是利用化學(xué)方法在絕緣孔壁上沉積上一層薄銅.流程:粗磨→掛板→沉銅自動線→下板→浸%稀H2SO4→加厚銅圖形轉(zhuǎn)移目的:圖形轉(zhuǎn)移是生產(chǎn)菲林上的圖像轉(zhuǎn)移到板上。流程:(藍(lán)油流程):磨板→印第Y面→烘干→印第二面→烘干→爆光→沖影→檢查;(干膜流程):麻板→壓膜→靜置→對位→曝光→靜置→沖影→檢查圖形電鍍目的:圖形電鍍是在線路圖形裸露的銅皮上或孔壁上電鍍一層達(dá)到要求厚度的銅層與要求厚度的金鎳或錫層。流程:上板→除油→水洗二次→微蝕→水洗→酸洗→鍍銅→水洗→浸酸→鍍錫→水洗→下板退膜目的:用NaOH溶液退去抗電鍍覆蓋膜層使非線路銅層裸露出來。流程:水膜:插架→浸堿→沖洗→擦洗→過機(jī);干膜:放板→過機(jī)蝕刻目的:蝕刻是利用化學(xué)反應(yīng)法將非線路部位的銅層腐蝕去。綠油目的:綠油是將綠油菲林的圖形轉(zhuǎn)移到板上,起到保護(hù)線路和阻止焊接零件時線路上錫的作用。流程:磨板→印感光綠油→鋦板→曝光→沖影;磨板→印第Y面→烘板→印第二面→烘板字符目的:字符是提供的一種便于辯認(rèn)的標(biāo)記。流程:綠油終鋦后→冷卻靜置→調(diào)網(wǎng)→印字符→后鋦鍍金手指目的:在插頭手指上鍍上一層要求厚度的鎳金層,使之更具有硬度的耐磨性。流程:上板→除油→水洗兩次→微蝕→水洗兩次→酸洗→鍍銅→水洗→鍍鎳→水洗→鍍金鍍錫板 (并列的一種工藝)目的:噴錫是在未覆蓋阻焊油的裸露銅面上噴上一層鉛錫,以保護(hù)銅面不蝕氧化,以保證具有良好的焊接性能.流程:微蝕→風(fēng)干→預(yù)熱→松香涂覆→焊錫涂覆→熱風(fēng)平整→風(fēng)冷→洗滌風(fēng)干成型目的:通過模具沖壓或數(shù)控鑼機(jī)鑼出客戶所需要的形狀成型的方法有機(jī)鑼,啤板,手鑼,手切說明:數(shù)據(jù)鑼機(jī)板與啤板的精確度較高,手鑼其次,手切板最低具只能做一些簡單的外形.測試目的:通過電子00%測試,檢測目視不易發(fā)現(xiàn)到的開路,短路等影響功能性之缺陷.流程:上模→放板→測試→合格→FQC目檢→不合格→修理→返測試→OK→REJ→報廢終檢目的:通過00%目檢板件外觀缺陷,并對輕微缺陷進(jìn)行修理,避免有問題及缺陷板件流出.具體工作流程:來料→查看資料→目檢→合格→FQA抽查→合格→包裝→不合格→處理→檢查OKa

安徽PCB打樣一個高明的CAD工程師需要做的是:如何綜合考慮各方意見,達(dá)到最佳結(jié)合點(diǎn)。以下為EDADOC專家根據(jù)個人在通訊產(chǎn)品PCB設(shè)計的多年經(jīng)驗(yàn),開發(fā)PCB打樣所總結(jié)出來的層疊設(shè)計參考,與大家共享。 PCB層疊設(shè)計基本原則 CAD工程師在完成布局(或預(yù)布局)后,重點(diǎn)對本板的布線瓶徑處進(jìn)行分析,再結(jié)合EDA軟件關(guān)于布線密度(PIN/RAT)的報告參數(shù)、綜合本板諸如差分線、敏感信號線、特殊拓?fù)浣Y(jié)構(gòu)等有特殊布線要求的信號數(shù)量、種類確定布線層數(shù);再根據(jù)單板的電源、地的種類、分布、有特殊布線需求的信號層數(shù),綜合單板的性能指標(biāo)要求與成本承受能力,確定單板的電源、地的層數(shù)以及它們與信號層的相對排布位置。單板層的排布一般原則:A)與元件面相鄰的層為地平面,提供器件屏蔽層以及為頂層布線提供回流平面;B)所有信號層盡可能與地平面相鄰(確保關(guān)鍵信號層與地平面相鄰);C)主電源盡可能與其對應(yīng)地相鄰;D)盡量避免兩信號層直接相鄰;

如果阻抗變化只發(fā)生一次,例如線寬從8mil變到6mil后,一直保持6mil寬度這種情況,要達(dá)到突變處信號反射噪聲不超過電壓擺幅的5%這一噪聲預(yù)算要求,阻抗變化必須小于10%。這有時很難做到,以 FR4板材上微帶線的情況為例,我們計算一下。如果線寬8mil,線條和參考平面之間的厚度為4mil,特性阻抗為46.5歐姆。線寬變化到6mil后特性阻抗變成54.2歐姆,阻抗變化率達(dá)到了20%。反射信號的幅度必然超標(biāo)。至于對信號造成多大影響,還和信號上升時間和驅(qū)動端到反射點(diǎn)處信號的時延有關(guān)。但至少這是一個潛在的問題點(diǎn)。幸運(yùn)的是這時可以通過阻抗匹配端接解決問題。如果阻抗變化發(fā)生兩次,例如線寬從8mil變到6mil后,拉出2cm后又變回8mil。那么在2cm長6mil寬線條的兩個端點(diǎn)處都會發(fā)生反射,一次是阻抗變大,發(fā)生正反射,接著阻抗變小,發(fā)生負(fù)反射。如果兩次反射間隔時間足夠短,兩次反射就有可能相互抵消,從而減小影響。假設(shè)傳輸信號為1V,第Y次正反射有0.2V被反射,1.2V繼續(xù)向前傳輸,第二次反射有 -0.2*1.2 = 0.24v被反射回。再假設(shè)6mil線長度極短,兩次反射幾乎同時發(fā)生,那么總的反射電壓只有0.04V,小于5%這一噪聲預(yù)算要求。因此,這種反射是否影響信號,有多大影響,和阻抗變化處的時延以及信號上升時間有關(guān)。研究及實(shí)驗(yàn)表明,只要阻抗變化處的時延小于信號上升時間的20%,反射信號就不會造成問題。如果信號上升時間為1ns,那么阻抗變化處的時延小于0.2ns對應(yīng)1.2英寸,反射就不會產(chǎn)生問題。也就是說,對于本例情況,6mil寬走線的長度只要小于3cm就不會有問題。

從IC芯片的發(fā)展及封裝形式來看,芯片體積越來越小、引腳數(shù)越來越多;同時,由于近年來IC工藝的發(fā)展,使得其速度也越來越高。這就帶來了一個問題,即電子設(shè)計的體積減小導(dǎo)致電路的布局布線密度變大,而同時信號的頻率還在提高,從而使得如何處理高速信號問題成為一個設(shè)計能否成功的關(guān)鍵因素。隨著電子系統(tǒng)中邏輯復(fù)雜度和時鐘頻率的迅速提高,信號邊沿不斷變陡,印刷電路板的線跡互連和板層特性對系統(tǒng)電氣性能的影響也越發(fā)重要。對于低頻設(shè)計,線跡互連和板層的影響可以不考慮,但當(dāng)頻率超過50 MHz時,互連關(guān)系必須考慮,而在*定系統(tǒng)性能時還必須考慮印刷電路板板材的電參數(shù)。因此,高速系統(tǒng)的設(shè)計必須面對互連延遲引起的時序問題以及串?dāng)_、傳輸線效應(yīng)等信號完整性(Signal Integrity,SI)問題。當(dāng)硬件工作頻率增高后,每一根布線網(wǎng)絡(luò)上的傳輸線都可能成為發(fā)射天線,對其他電子設(shè)備產(chǎn)生電磁輻射或與其他設(shè)備相互干擾,從而使硬件時序邏輯產(chǎn)生混亂。電磁兼容性(Electromagnetic Compatibility,EMC)的標(biāo)準(zhǔn)提出了解決硬件實(shí)際布線網(wǎng)絡(luò)可能產(chǎn)生的電磁輻射干擾以及本身抵抗外部電磁干擾的基本要求。1 高速數(shù)字電路設(shè)計的幾個基本概念在高速數(shù)字電路中,由于串?dāng)_、反射、過沖、振蕩、地彈、偏移等信號完整性問題,本來在低速電路中無需考慮的因素在這里就顯得格外重要;另外,隨著現(xiàn)有電氣系統(tǒng)耦合結(jié)構(gòu)越來越復(fù)雜,電磁兼容性也變成了一個不能不考慮的問題。要解決高速電路設(shè)計的問題,首先需要真正明白高速信號的概念。高速不是就頻率的高低來說的,而是由信號的邊沿速度決定的,一般認(rèn)為上升時間小于4倍信號傳輸延遲時可視為高速信號。即使在工作頻率不高的系統(tǒng)中,也會出現(xiàn)信號完整性的問題。這是由于隨著集成電路工藝的提高,所用器件I/O端口的信號邊沿比以前更陡更快,因此在工作時鐘不高的情況下也屬于高速器件,隨之帶來了信號完整性的種種問題。