北京廠家貼片SMT一、PCB沉金采用的是化學沉積的方法,通過化學氧化還原反應的方法生成一層鍍層,一般厚度較厚,廠家貼片SMT是化學鎳金金層沉積方法的一種,可以達到較厚的金層。二、PCB鍍金采用的是電解的原理,也叫電鍍方式。其他金屬表面處理也多數采用的是電鍍方式。在實際產品應用中,90%的金板是沉金板,因為鍍金板焊接性差是他的致命缺點,也是導致很多公司放棄鍍金工藝的直接原因!沉金工藝在印制線路表面上沉積顏色穩定,光亮度好,鍍層平整,可焊性良好的鎳金鍍層。基本可分為四個階段:前處理(除油,微蝕,活化、后浸),沉鎳,沉金,后處理(廢金水洗,DI水洗,烘干)。沉金厚度在0.025-0.1um間。金應用于電路板表面處理,因為金的導電性強,抗氧化性好,壽命長,而鍍金板與沉金板最根本的區別在于,鍍金是硬金(耐磨),沉金是軟金(不耐磨)。1、沉金與鍍金所形成的晶體結構不一樣,沉金對于金的厚度比鍍金要厚很多,沉金會呈金黃色,較鍍金來說更黃(這是區分鍍金和沉金的方法之一),鍍金的會稍微發白(鎳的顏色)。2、沉金與鍍金所形成的晶體結構不一樣,沉金相對鍍金來說更容易焊接,不會造成焊接不良。沉金板的應力更易控制,對有邦定的產品而言,更有利于邦定的加工。同時也正因為沉金比鍍金軟,所以沉金板做金手指不耐磨(沉金板的缺點)。3、PCB沉金板只有焊盤上有鎳金,趨膚效應中信號的傳輸是在銅層不會對信號有影響。4、沉金較鍍金來說晶體結構更致密,不易產成氧化。5、隨著電路板加工精度要求越來越高,線寬、間距已經到了0.1mm以下。鍍金則容易產生金絲短路。沉金板只有焊盤上有鎳金,所以不容易產成金絲短路。

一個高明的CAD工程師需要做的是:如何綜合考慮各方意見,達到最佳結合點。以下為EDADOC專家根據個人在通訊產品PCB設計的多年經驗,所總結出來的層疊設計參考,與大家共享。 PCB層疊設計基本原則 CAD工程師在完成布局(或預布局)后,重點對本板的布線瓶徑處進行分析,再結合EDA軟件關于布線密度(PIN/RAT)的報告參數、綜合本板諸如差分線、敏感信號線、特殊拓撲結構等有特殊布線要求的信號數量、種類確定布線層數;再根據單板的電源、地的種類、分布、有特殊布線需求的信號層數,綜合單板的性能指標要求與成本承受能力,確定單板的電源、地的層數以及它們與信號層的相對排布位置。單板層的排布一般原則:A)與元件面相鄰的層為地平面,提供器件屏蔽層以及為頂層布線提供回流平面;B)所有信號層盡可能與地平面相鄰(確保關鍵信號層與地平面相鄰);C)主電源盡可能與其對應地相鄰;D)盡量避免兩信號層直接相鄰;

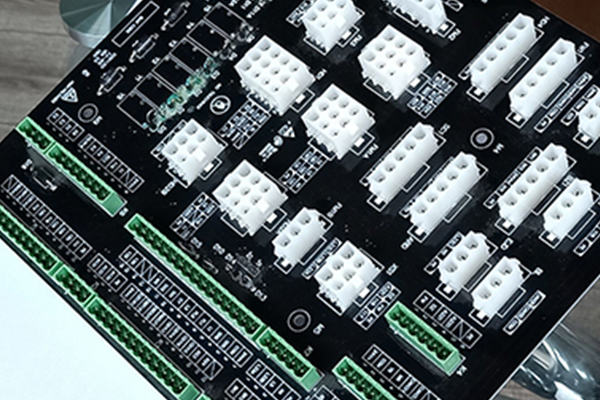

線路板打樣本身的基板是由隔熱、并不易彎曲的材質所制作成。在表層能夠看到的很小線路材料是銅箔,原本銅箔是覆蓋在整個線路板板上的,并且在生產過程中部份被蝕刻掉,留下來的就變成網狀的細小線路了。這些線路被稱作導線或稱布線,用來提供線路板上零件的電路連接。通常PCB板的顏色都是棕色或是綠色,這是阻焊漆的顏色。是絕緣的防護層,可以保護銅線,也可以防止零件被焊到錯誤的地方。現在顯卡和主板上都是多層板,很大程度上可以增加布線的面積。多層板用上了更多單或雙面的布線板,并在每層板間放進一層絕緣層后壓合。PCB板的層數就代表了有幾層獨立的布線層,通常層數都是偶數,并且包含最外側的兩層,常見的PCB板一般是4~8層的結構。很多PCB板的層數可以通過觀看PCB板的切面看出來。但實際上,沒有人能有這么好的眼力。所以,下面再教大家一種方法。多層板打樣的電路連接是通過埋孔和盲孔技術,主板和顯示卡大多使用4層的PCB板,也有些是采用6、8層,甚至10層的PCB板。要想看出是PCB有多少層,通過觀察導孔就可以辯識,因為在主板和顯示卡上使用的4層板是第1、第4層走線,其他幾層另有用途(地線和電源)。所以,同雙層板一樣,導孔會打穿PCB板。如果有的導孔在PCB板正面出現,卻在反面找不到,那么就一定是6/8層板了。如果PCB板的正反面都能找到相同的導孔,自然就是4層板了。把主板對著有光處,看到導孔的位置,如果能透光,這就是8/6層板,否就是四層板.

相信對做硬件的工程師,畢業開始進公司時,在設計PCB時,老工程師都會對他說,PCB走線不要走直角,走線一定要短,電容一定要就近擺放等等。但是一開始我們可能都不了解為什么這樣做,就憑他們的幾句經驗對我們來說是遠遠不夠的哦,當然如果你沒有注意這些細節問題,今后又犯了,可能又會被他們罵,“都說了多少遍了電容一定要就近擺放,放遠了起不到效果等等”,往往經驗告訴我們其實那些老工程師也是只有一部分人才真正掌握其中的奧妙,我們一開始不會也不用難過,多看看資料很快就能掌握的。直到被罵好幾次后我們回去找相關資料,為什么設計PCB電容要就近擺放呢,等看了資料后就能了解一些,可是網上的資料很雜散,很少能找到一個很全方面講解的。下面這些內容是我轉載的一篇關于電容去耦半徑的講解,相信你看了之后可以很牛x的回答和避免類似問題的發生。老師問: 為什么去耦電容就近擺放呢?學生答: 因為它有有效半徑哦,放的遠了失效的。電容去耦的一個重要問題是電容的去耦半徑。大多數資料中都會提到電容擺放要盡量靠近芯片,多數資料都是從減小回路電感的角度來談這個擺放距離問題。確實,減小電感是一個重要原因,但是還有一個重要的原因大多數資料都沒有提及,那就是電容去耦半徑問題。如果電容擺放離芯片過遠,超出了它的去耦半徑,電容將失去它的去耦的作用。理解去耦半徑最好的辦法就是考察噪聲源和電容補償電流之間的相位關系。當芯片對電流的需求發生變化時,會在電源平面的一個很小的局部區域內產生電壓擾動,電容要補償這一電流(或電壓),就必須先感知到這個電壓擾動。信號在介質中傳播需要一定的時間,因此從發生局部電壓擾動到電容感知到這一擾動之間有一個時間延遲。同樣,電容的補償電流到達擾動區也需要一個延遲。因此必然造成噪聲源和電容補償電流之間的相位上的不一致。

隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性已經成為高速數字PCB設計必須關心的問題之一。元器件和PCB板的參數、元器件在PCB板上的布局、高速信號的布線等因素,都會引起信號完整性問題,導致系統工作不穩定,甚至完全不工作。如何在PCB板的設計過程中充分考慮到信號完整性的因素,并采取有效的控制措施,已經成為當今PCB設計業界中的一個熱門課題。基于信號完整性計算機分析的高速數字PCB板設計方法能有效地實現PCB設計的信號完整性。1. 信號完整性問題概述信號完整性(SI)是指信號在電路中以正確的時序和電壓作出響應的能力。如果電路中信號能夠以要求的時序、持續時間和電壓幅度到達IC,則該電路具有較好的信號完整性。反之,當信號不能正常響應時,就出現了信號完整性問題。從廣義上講,信號完整性問題主要表現為5個方面:延遲、反射、串擾、同步切換噪聲(SSN)和電磁兼容性(EMI)。延遲是指信號在PCB板的導線上以有限的速度傳輸,信號從發送端發出到達接收端,其間存在一個傳輸延遲。信號的延遲會對系統的時序產生影響,在高速數字系統中,傳輸延遲主要取決于導線的長度和導線周圍介質的介電常數。另外,當PCB板上導線(高速數字系統中稱為傳輸線)的特征阻抗與負載阻抗不匹配時,信號到達接收端后有一部分能量將沿著傳輸線反射回去,使信號波形發生畸變,甚至出現信號的過沖和下沖。信號如果在傳輸線上來回反射,就會產生振鈴和環繞振蕩。