一個(gè)布局是否合理沒(méi)有判斷標(biāo)準(zhǔn),可以采用一些相對(duì)簡(jiǎn)單的標(biāo)準(zhǔn)來(lái)判斷布局的優(yōu)劣。最常用的標(biāo)準(zhǔn)就是使飛線總長(zhǎng)度盡可能短。一般來(lái)說(shuō),飛線總長(zhǎng)度越短,意味著布線總長(zhǎng)度也是越短(注意:這只是相對(duì)于大多數(shù)情況是正確的,并不是完全正確);走線越短,走線所占據(jù)的印制板面積也就越小,布通率越高。在走線盡可能短的同時(shí),還必須考慮布線密度的問(wèn)題。如何布局才能使飛線總長(zhǎng)度最短并且保證布局密度不至于過(guò)高而不能實(shí)現(xiàn)是個(gè)很復(fù)雜的問(wèn)題。因?yàn)椋{(diào)整布局就是調(diào)整封裝的放置位置,一個(gè)封裝的焊盤(pán)往往和幾個(gè)甚至幾十個(gè)網(wǎng)絡(luò)同時(shí)相關(guān)聯(lián),減小一個(gè)網(wǎng)絡(luò)飛線長(zhǎng)度可能會(huì)增長(zhǎng)另一個(gè)網(wǎng)絡(luò)的飛線長(zhǎng)度。如何能夠調(diào)整封裝的位置到最佳點(diǎn)實(shí)在給不出太實(shí)用的標(biāo)準(zhǔn),實(shí)際操作時(shí),主要依靠設(shè)計(jì)者的經(jīng)驗(yàn)觀查屏幕顯示的飛線是否簡(jiǎn)捷、有序和計(jì)算出的總長(zhǎng)度是否最短。飛線是手工布局和布線的主要參考標(biāo)準(zhǔn),手工調(diào)整布局時(shí)盡量使飛線走最短路徑,手工布線時(shí)常常按照飛線指示的路徑連接各個(gè)焊盤(pán)。Protel的飛線優(yōu)化算法可以有效地解決飛線連接的最短路徑問(wèn)題。飛線的連接策略Protel提供了兩種飛線連接方式供使用者選擇:順序飛線和最短樹(shù)飛線。在布線參數(shù)設(shè)置中的飛線模式頁(yè)可以設(shè)置飛線連接策略,應(yīng)該選擇最短樹(shù)策略。動(dòng)態(tài)飛線在有關(guān)飛線顯示和控制一節(jié)中已經(jīng)講到: 執(zhí)行顯示網(wǎng)絡(luò)飛線、顯示封裝飛線和顯示全部飛線命令之一后飛線顯示開(kāi)關(guān)打開(kāi),執(zhí)行隱含全部飛線命令后飛線顯示開(kāi)關(guān)關(guān)閉。

廠家PCB抄板設(shè)計(jì)在PCB板的設(shè)計(jì)當(dāng)中,可以通過(guò)分層、恰當(dāng)?shù)牟季植季€和安裝實(shí)現(xiàn)PCB的抗ESD設(shè)計(jì)。在設(shè)計(jì)過(guò)程中,廠家PCB抄板設(shè)計(jì)加工廠通過(guò)預(yù)測(cè)可以將絕大多數(shù)設(shè)計(jì)修改僅限于增減元器件。通過(guò)調(diào)整PCB布局布線,能夠很好地防范ESD。以下是一些常見(jiàn)的防范措施。1、盡可能使用多層PCB相對(duì)于雙面PCB而言,地平面和電源平面,以及排列緊密的信號(hào)線-地線間距能夠減小共模阻抗和感性耦合,使之達(dá)到雙面PCB的1/10到1/100。盡量地將每一個(gè)信號(hào)層都緊靠一個(gè)電源層或地線層。對(duì)于頂層和底層表面都有元器件、具有很短連接線以及許多填充地的高密度PCB,可以考慮使用內(nèi)層線。2、對(duì)于雙面PCB來(lái)說(shuō),要采用緊密交織的電源和地柵格。電源線緊靠地線,在垂直和水平線或填充區(qū)之間,要盡可能多地連接。一面的柵格尺寸小于等于60mm,如果可能,柵格尺寸應(yīng)小于13mm。3、確保每一個(gè)電路盡可能緊湊。4、盡可能將所有連接器都放在一邊。5、在每一層的機(jī)箱地和電路地之間,要設(shè)置相同的“隔離區(qū)”;如果可能,保持間隔距離為0.64mm。6、PCB裝配時(shí),不要在頂層或者底層的焊盤(pán)上涂覆任何焊料。使用具有內(nèi)嵌墊圈的螺釘來(lái)實(shí)現(xiàn)PCB與金屬機(jī)箱/屏蔽層或接地面上支架的緊密接觸。

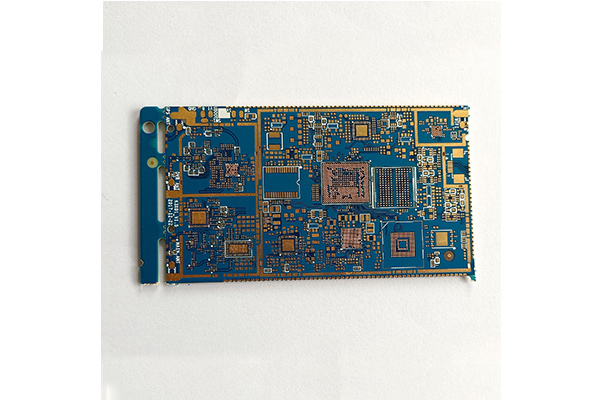

【第Y招】多層板布線高頻電路往往集成度較高,布線密度大,采用多層板既是布線所必須,也是降低干擾的有效手段。在PCB Layout階段,合理的選擇一定層數(shù)的印制板尺寸,能充分利用中間層來(lái)設(shè)置屏蔽,更好地實(shí)現(xiàn)就近接地,并有效地降低寄生電感和縮短信號(hào)的傳輸長(zhǎng)度,同時(shí)還能大幅度地降低信號(hào)的交叉干擾等,所有這些方法都對(duì)高頻電路的可靠性有利。有資料顯示,同種材料時(shí),四層板要比雙面板的噪聲低20dB。但是,同時(shí)也存在一個(gè)問(wèn)題,PCB半層數(shù)越高,制造工藝越復(fù)雜,單位成本也就越高,這就要求我們?cè)谶M(jìn)行PCB Layout時(shí),除了選擇合適的層數(shù)的PCB板,還需要進(jìn)行合理的元器件布局規(guī)劃,并采用正確的布線規(guī)則來(lái)完成設(shè)計(jì)。 【第二招】高速電子器件管腳間的引線彎折越少越好 高頻電路布線的引線最好采用全直線,需要轉(zhuǎn)折,可用45度折線或者圓弧轉(zhuǎn)折,這種要求在低頻電路中僅僅用于提高銅箔的固著強(qiáng)度,而在高頻電路中,滿足這一要求卻可以減少高頻信號(hào)對(duì)外的發(fā)射和相互間的耦合。 【第三招】高頻電路器件管腳間的引線越短越好 信號(hào)的輻射強(qiáng)度是和信號(hào)線的走線長(zhǎng)度成正比的,高頻的信號(hào)引線越長(zhǎng),它就越容易耦合到靠近它的元器件上去,所以對(duì)于諸如信號(hào)的時(shí)鐘、晶振、DDR的數(shù)據(jù)、LVDS線、USB線、HDMI線等高頻信號(hào)線都是要求盡可能的走線越短越好。 【第四招】高頻電路器件管腳間的引線層間交替越少越好 所謂“引線的層間交替越少越好”是指元件連接過(guò)程中所用的過(guò)孔(Via)越少越好。據(jù)側(cè),一個(gè)過(guò)孔可帶來(lái)約0.5pF的分布電容,減少過(guò)孔數(shù)能顯著提高速度和減少數(shù)據(jù)出錯(cuò)的可能性。

PCB上的任何一條走線在通過(guò)高頻信號(hào)的情況下都會(huì)對(duì)該信號(hào)造成時(shí)延時(shí),蛇形走線的主要作用是補(bǔ)償“同一組相關(guān)”信號(hào)線中延時(shí)較小的部分,這些部分通常是沒(méi)有或比其它信號(hào)少通過(guò)另外的邏輯處理;最典型的就是時(shí)鐘線,通常它不需經(jīng)過(guò)任何其它邏輯處理,因而其延時(shí)會(huì)小于其它相關(guān)信號(hào)。高速數(shù)字PCB板的等線長(zhǎng)是為了使各信號(hào)的延遲差保持在一個(gè)范圍內(nèi),保證系統(tǒng)在同一周期內(nèi)讀取的數(shù)據(jù)的有效性(延遲差超過(guò)一個(gè)時(shí)鐘周期時(shí)會(huì)錯(cuò)讀下一周期的數(shù)據(jù)),一般要求延遲差不超過(guò)1/4時(shí)鐘周期,單位長(zhǎng)度的線延遲差也是固定的,延遲跟線寬,線長(zhǎng),銅厚,板層結(jié)構(gòu)有關(guān),但線過(guò)長(zhǎng)會(huì)增大分布電容和分布電感,使信號(hào)質(zhì)量,所以時(shí)鐘IC引腳一般都接RC端接,但蛇形走線并非起電感的作用,相反的,電感會(huì)使信號(hào)中的上升元中的高次諧波相移,造成信號(hào)質(zhì)量惡化,所以要求蛇形線間距最少是線寬的兩倍,信號(hào)的上升時(shí)間越小就越易受分布電容和分布電感的影響.因?yàn)閼?yīng)用場(chǎng)合不同具不同的作用,如果蛇形走線在電腦板中出現(xiàn),其主要起到一個(gè)濾波電感的作用,提高電路的抗干擾能力,電腦主機(jī)板中的蛇形走線,主要用在一些時(shí)鐘信號(hào)中,如CIClk,AGPClk,它的作用有兩點(diǎn):1、阻抗匹配2、濾波電感。對(duì)一些重要信號(hào),如INTEL HUB架構(gòu)中的HUBLink,一共13根,跑233MHz,要求必須嚴(yán)格等長(zhǎng),以消除時(shí)滯造成的隱患,繞線是解決辦法。一般來(lái)講,蛇形走線的線距>=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI33MHzClock的線長(zhǎng)要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等.

一個(gè)高明的CAD工程師需要做的是:如何綜合考慮各方意見(jiàn),達(dá)到最佳結(jié)合點(diǎn)。以下為EDADOC專家根據(jù)個(gè)人在通訊產(chǎn)品PCB設(shè)計(jì)的多年經(jīng)驗(yàn),所總結(jié)出來(lái)的層疊設(shè)計(jì)參考,與大家共享。 PCB層疊設(shè)計(jì)基本原則 CAD工程師在完成布局(或預(yù)布局)后,重點(diǎn)對(duì)本板的布線瓶徑處進(jìn)行分析,再結(jié)合EDA軟件關(guān)于布線密度(PIN/RAT)的報(bào)告參數(shù)、綜合本板諸如差分線、敏感信號(hào)線、特殊拓?fù)浣Y(jié)構(gòu)等有特殊布線要求的信號(hào)數(shù)量、種類(lèi)確定布線層數(shù);再根據(jù)單板的電源、地的種類(lèi)、分布、有特殊布線需求的信號(hào)層數(shù),綜合單板的性能指標(biāo)要求與成本承受能力,確定單板的電源、地的層數(shù)以及它們與信號(hào)層的相對(duì)排布位置。單板層的排布一般原則:A)與元件面相鄰的層為地平面,提供器件屏蔽層以及為頂層布線提供回流平面;B)所有信號(hào)層盡可能與地平面相鄰(確保關(guān)鍵信號(hào)層與地平面相鄰);C)主電源盡可能與其對(duì)應(yīng)地相鄰;D)盡量避免兩信號(hào)層直接相鄰;

在基于信號(hào)完整性計(jì)算機(jī)分析的PCB設(shè)計(jì)方法中,最為核心的部分就是PCB板級(jí)信號(hào)完整性模型的建立,這是與傳統(tǒng)的設(shè)計(jì)方法的區(qū)別之處。SI模型的正確性將決定設(shè)計(jì)的正確性,而SI模型的可建立性則決定了這種設(shè)計(jì)方法的可行性。目前構(gòu)成器件模型的方法有兩種:一種是從元器件的電學(xué)工作特性出發(fā),把元器件看成‘黑盒子’,測(cè)量其端口的電氣特性,提取器件模型,而不涉及器件的工作原理,稱為行為級(jí)模型。這種模型的代表是IBIS模型和S參數(shù)。其優(yōu)點(diǎn)是建模和使用簡(jiǎn)單方便,節(jié)約資源,適用范圍廣泛,特別是在高頻、非線性、大功率的情況下行為級(jí)模型是一個(gè)選擇。缺點(diǎn)是精度較差,一致性不能保證,受測(cè)試技術(shù)和精度的影響。另一種是以元器件的工作原理為基礎(chǔ),從元器件的數(shù)學(xué)方程式出發(fā),得到的器件模型及模型參數(shù)與器件的物理工作原理有密切的關(guān)系。SPICE 模型是這種模型中應(yīng)用最廣泛的一種。其優(yōu)點(diǎn)是精度較高,特別是隨著建模手段的發(fā)展和半導(dǎo)體工藝的進(jìn)步和規(guī)范,人們已可以在多種級(jí)別上提供這種模型,滿足不同的精度需要。缺點(diǎn)是模型復(fù)雜,計(jì)算時(shí)間長(zhǎng)。一般驅(qū)動(dòng)器和接收器的模型由器件廠商提供,傳輸線的模型通常從場(chǎng)分析器中提取,封裝和連接器的模型即可以由場(chǎng)分析器提取,又可以由制造廠商提供。在電子設(shè)計(jì)中已經(jīng)有多種可以用于PCB板級(jí)信號(hào)完整性分析的模型,其中最為常用的有三種,分別是SPICE、IBIS和Verilog-AMS、VHDL-AMS。