1、PCB分板機對于運轉問題的原因:蓄電池沒有充足電力,蓄電池和啟動電機之間的連接斷開。蓄電池或接線卡子出現的氧化的現象;電磁開關與兩大接線柱接觸不良或是導流片被嚴重燒蝕;電刷出現磨損、折斷或是電刷卡在刷架中;電刷整流器間存在油污或是整流片的嚴重燒蝕。2、繞組部分短路或斷路:有三個原因會出現這種情況,一是電樞繞組或是換向器片出現脫焊現象,二是軸承或銅套出現磨損導致轉子掃膛,三是在安裝的時候4個電刷的位置裝錯了或是新換的軸套間隙過大。PCB分板機啟動時空轉:撥叉安裝不正確,撥叉滑柱裝置在挪動襯套內讓電動機齒輪不可能與撥叉一同轉動。3.PCB分板機啟動電機就會轉動。電磁開關鐵芯和接盤推桿間間的間隙太大會造成單向離合器打滑,無法帶動飛輪齒圈轉動。啟動電機齒輪一旦嚴重磨損,就會無法與飛輪齒圈很好地磨合。電磁開關常吸常開,是指在按下啟動開關后,電磁開關的鐵芯剛被吸上去就會馬上脫下來,脫下來后又會被吸上去,然后又馬上脫下來,達不到啟動發起機的效果1。呈現這種毛病現象的常見緣由是堅持線圈斷路。

通訊與計算機技術的高速發展使得高速PCB設計進入了千兆位領域,新的高速器件應用使得如此高的速率在背板和單板上的長距離傳輸成為可能,但與此同時,PCB設計中的信號完整性問題(SI)、電源完整性以及電磁兼容方面的問題也更加突出。信號完整性是指信號在信號線上傳輸的質量,主要問題包括反射、振蕩、時序、地彈和串擾等。信號完整性差不是由某個單一因素導致,而是板級設計中多種因素共同引起。在千兆位設備的PCB板設計中,一個好的信號完整性設計要求工程師全面考慮器件、傳輸線互聯方案、電源分配以及EMC方面的問題。高速PCB設計EDA工具已經從單純的仿真驗證發展到設計和驗證相結合,幫助設計者在設計早期設定規則以避免錯誤而不是在設計后期發現問題。隨著數據速率越來越高設計越來越復雜,高速PCB系統分析工具變得更加必要,這些工具包括時序分析、信號完整性分析、設計空間參數掃描分析、EMC設計、電源系統穩定性分析等。這里我們將著重討論在千兆位設備PCB設計中信號完整性分析應考慮的一些問題。高速器件與器件模型盡管千兆位發送與接收元器件供應商會提供有關芯片的設計資料,但是器件供應商對于新器件信號完整性的了解也存在一個過程,這樣器件供應商給出的設計指南可能并不成熟,還有就是器件供應商給出的設計約束條件通常都是非常苛刻的,對設計工程師來說要滿足所有的設計規則會非常困難。所以就需要信號完整性工程師運用仿真分析工具對供應商的約束規則和實際設計進行分析,考察和優化元器件選擇、拓撲結構、匹配方案、匹配元器件的值,并最終開發出確保信號完整性的PCB布局布線規則。因此,千兆位信號的精確仿真分析變得十分重要,而器件模型在信號完整性分析工作中的作用也越來越得到重視。

開發電路板組裝測試在PCB板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。在設計過程中,開發電路板組裝測試生產廠通過預測可以將絕大多數設計修改僅限于增減元器件。通過調整PCB布局布線,能夠很好地防范ESD。以下是一些常見的防范措施。1、盡可能使用多層PCB相對于雙面PCB而言,地平面和電源平面,以及排列緊密的信號線-地線間距能夠減小共模阻抗和感性耦合,使之達到雙面PCB的1/10到1/100。盡量地將每一個信號層都緊靠一個電源層或地線層。對于頂層和底層表面都有元器件、具有很短連接線以及許多填充地的高密度PCB,可以考慮使用內層線。2、對于雙面PCB來說,要采用緊密交織的電源和地柵格。電源線緊靠地線,在垂直和水平線或填充區之間,要盡可能多地連接。一面的柵格尺寸小于等于60mm,如果可能,柵格尺寸應小于13mm。3、確保每一個電路盡可能緊湊。4、盡可能將所有連接器都放在一邊。5、在每一層的機箱地和電路地之間,要設置相同的“隔離區”;如果可能,保持間隔距離為0.64mm。6、PCB裝配時,不要在頂層或者底層的焊盤上涂覆任何焊料。使用具有內嵌墊圈的螺釘來實現PCB與金屬機箱/屏蔽層或接地面上支架的緊密接觸。

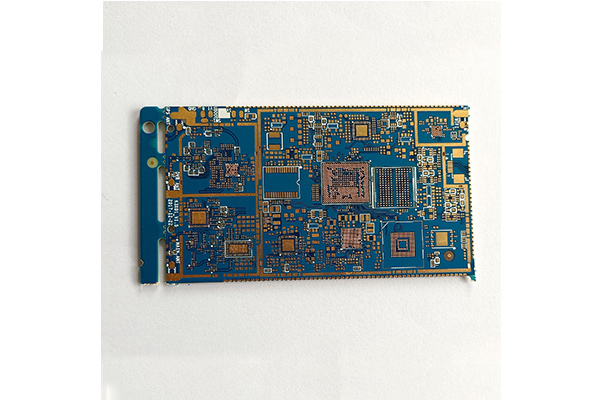

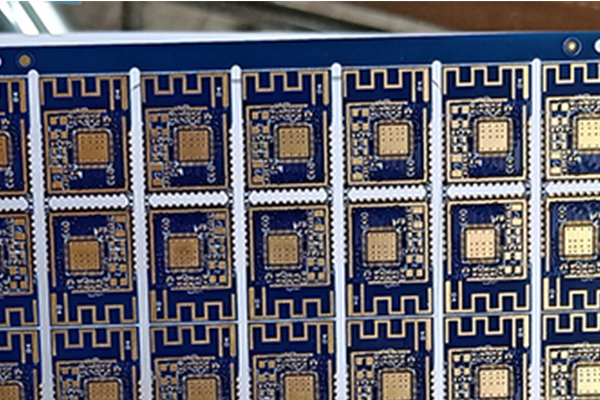

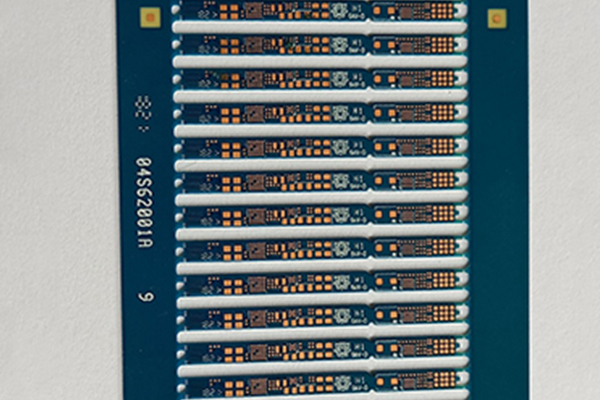

一、PCB沉金采用的是化學沉積的方法,通過化學氧化還原反應的方法生成一層鍍層,一般厚度較厚,是化學鎳金金層沉積方法的一種,可以達到較厚的金層。二、PCB鍍金采用的是電解的原理,也叫電鍍方式。其他金屬表面處理也多數采用的是電鍍方式。在實際產品應用中,90%的金板是沉金板,因為鍍金板焊接性差是他的致命缺點,也是導致很多公司放棄鍍金工藝的直接原因!沉金工藝在印制線路表面上沉積顏色穩定,光亮度好,鍍層平整,可焊性良好的鎳金鍍層。基本可分為四個階段:前處理(除油,微蝕,活化、后浸),沉鎳,沉金,后處理(廢金水洗,DI水洗,烘干)。沉金厚度在0.025-0.1um間。金應用于電路板表面處理,因為金的導電性強,抗氧化性好,壽命長,而鍍金板與沉金板最根本的區別在于,鍍金是硬金(耐磨),沉金是軟金(不耐磨)。1、沉金與鍍金所形成的晶體結構不一樣,沉金對于金的厚度比鍍金要厚很多,沉金會呈金黃色,較鍍金來說更黃(這是區分鍍金和沉金的方法之一),鍍金的會稍微發白(鎳的顏色)。2、沉金與鍍金所形成的晶體結構不一樣,沉金相對鍍金來說更容易焊接,不會造成焊接不良。沉金板的應力更易控制,對有邦定的產品而言,更有利于邦定的加工。同時也正因為沉金比鍍金軟,所以沉金板做金手指不耐磨(沉金板的缺點)。3、PCB沉金板只有焊盤上有鎳金,趨膚效應中信號的傳輸是在銅層不會對信號有影響。4、沉金較鍍金來說晶體結構更致密,不易產成氧化。5、隨著電路板加工精度要求越來越高,線寬、間距已經到了0.1mm以下。鍍金則容易產生金絲短路。沉金板只有焊盤上有鎳金,所以不容易產成金絲短路。6、沉金板只有焊盤上有鎳金,所以線路上的阻焊與銅層的結合更牢固。工程在作補償時不會對間距產生影響。7、對于要求較高的板子,平整度要求要好,一般就采用沉金,沉金一般不會出現組裝后的黑墊現象。沉金板的平整性與使用壽命較鍍金板要好。所以目前大多數工廠都采用了沉金工藝生產金板。但是沉金工藝比鍍金工藝成本更貴(含金量更高),所以依然還有大量的低價產品使用鍍金工藝。

隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性已經成為高速數字PCB設計必須關心的問題之一。元器件和PCB板的參數、元器件在PCB板上的布局、高速信號的布線等因素,都會引起信號完整性問題,導致系統工作不穩定,甚至完全不工作。如何在PCB板的設計過程中充分考慮到信號完整性的因素,并采取有效的控制措施,已經成為當今PCB設計業界中的一個熱門課題。基于信號完整性計算機分析的高速數字PCB板設計方法能有效地實現PCB設計的信號完整性。1. 信號完整性問題概述信號完整性(SI)是指信號在電路中以正確的時序和電壓作出響應的能力。如果電路中信號能夠以要求的時序、持續時間和電壓幅度到達IC,則該電路具有較好的信號完整性。反之,當信號不能正常響應時,就出現了信號完整性問題。從廣義上講,信號完整性問題主要表現為5個方面:延遲、反射、串擾、同步切換噪聲(SSN)和電磁兼容性(EMI)。延遲是指信號在PCB板的導線上以有限的速度傳輸,信號從發送端發出到達接收端,其間存在一個傳輸延遲。信號的延遲會對系統的時序產生影響,在高速數字系統中,傳輸延遲主要取決于導線的長度和導線周圍介質的介電常數。另外,當PCB板上導線(高速數字系統中稱為傳輸線)的特征阻抗與負載阻抗不匹配時,信號到達接收端后有一部分能量將沿著傳輸線反射回去,使信號波形發生畸變,甚至出現信號的過沖和下沖。信號如果在傳輸線上來回反射,就會產生振鈴和環繞振蕩。